# RF-BM-2340A2 And RF-BM-2340A2I CC2340R5 BLE5.3 or ZigBee 3.0 Wireless Module Hardware Specification

Version 1.1

Shenzhen RF-star Technology Co., Ltd.

Jun. 6<sup>th</sup>, 2024

All rights reserved. Those responsible for unauthorized reproduction will be prosecuted.

#### 1 Device Overview

## 1.1 Description

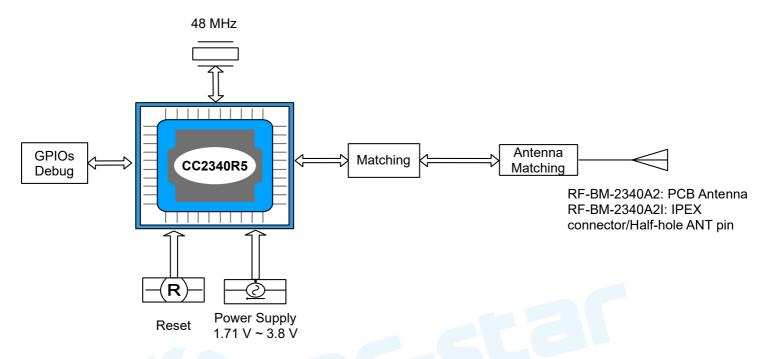

RF-BM-2340A2 and RF-BM-2340A2I are RF modules based on TI lower-power CC2340R5 SoC. They are multiprotocol 2.4 GHz wireless modules supporting Thread, ZigBee®, Bluetooth® 5.3 Low Energy, IEEE 802.15.4, and proprietary 2.4 GHz. The modules integrate a 48 MHz crystal, 512 kB of in-system Programmable Flash, 12 kB ROM for bootloader, and 36 kB of ultra-low leakage SRAM. The ARM® Cortex®-M0+ core application processor can operate at an extremely low current at flexible power modes. And the modules enable long-range and low-power applications using 8 dBm high-power with best-in-class transmit current consumption at 12 mA. They feature a small size, robust connection distance, and rigid reliability. The 1.27-mm half-hole pitch stamp stick makes the module more convenient for application and development. RF-BM-2340A2 has a high-performance PCB antenna, while RF-BM-2340A2I has an IPEX connector or a half-hole RF out interface option for the different needs of external antennas. The UART serial port protocol can also enable you to start your development with a quick path.

## 1.2 Key Features

- RF Features

- Bluetooth® 5.3 Low Energy

- Bluetooth Mesh (Low power node)

- ZigBee®

- Proprietary

- SimpleLink TI 15.4-Stack (2.4 GHz)

- TX power: up to +8 dBm with temperature compensation

- Excellent receiver sensitivity

- -102 dBm for Bluetooth 125 kbps (LE coded PHY)

- -99 dBm for Bluetooth 500 kbps (LE coded PHY)

- -96.5 dBm for Bluetooth 1 Mbps

- -92 dBm for Bluetooth 2 Mbps

- Wide Operation Range

- Power supply:

- → GLDO mode: 1.71 V ~ 3.8 V, recommend to

3.3 V

- ♦ DCDC mode: 2.2 V ~ 3.8 V, recommend to 3.3 V

- Operating temperature: -40 °C to +85 °C

- Storage temperature: -40 °C to +125 °C

- Frequency range: 2360 MHz ~ 2510 MHz

- Microcontroller

- Powerful 48 MHz ARM® Cortex®-M0+ processor

- Integrated Balun

- Support OTA upgrade

- Memory

- 512 kB of in-system programmable flash

- 12 kB of ROM for bootloader and drivers

- 36 kB of ultra-low leakage SRAM. Retained in standby mode

- Rich Peripherals

- 12 IO Pads

- ♦ 2 IO pads SWD, muxed with GPIOs

- ♦ Up to 10 DIOs (analog or digital IOs)

- 3 × 16-bit or 1 × 24-bit general-purpose timers,

Quadrature decode mode support

- 12-bit ADC, 1.2 Msps with external reference,

267 kbps with internal reference, up to 12 external ADC inputs

- 1× low power comparator

- 1 × UART

- 1 × SPI

- 1 × I<sup>2</sup>C

## www.rfstariot.com

- Real-time clock (RTC)

- Integrated temperature and battery monitor

- Watchdog timer

- Security Enablers

- AES 128-bit Crypto accelerator

- Random number generator from on-chip

## analog noise

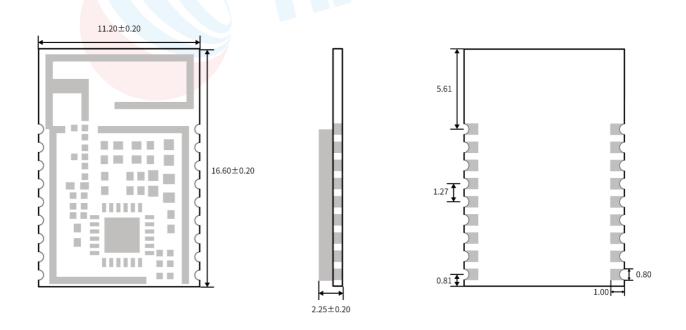

- Dimension:

- RF-BM-2340A2: 16.58 mm × 11.19 mm × 2.25 mm

- RF-BM-2340A2I: 15.20 mm × 11.19 mm × 2.25 mm

## 1.3 Applications

- Home healthcare

- Blood glucose monitors

- Blood pressure monitor

- CPAP machine

- Electronic thermometer

- Patient monitoring & diagnostics

- Medical sensor patches

- Personal care & Fitness

- Electric toothbrush

- Wearable fitness & activity monitor

- Building automation

- Building security systems

- Motion detector

- Electronic smart lock

- Door and window sensor

- · Garage door system

- Gateway

- HVAC

- Thermostat

- Wireless environmental sensor

- Fire safety system

- Smoke and heat detector

- Video surveillance

- IP network camera

- Lighting

- LED luminaire

- Lighting Control

- Daylight sensor, lighting sensor

- Wireless control

- Factory automation and control

- Retail automation & payment

- · Electronic point of sale

- Communication equipment

- · Wired networking

- Personal electronics

- Connected peripherals

- Consumer wireless module

- Pointing devices

- Keyboards and keypads

- Gaming

- Electronic and robotic toys

- Wearables (non-medical)

- Smart trackers

- Smart clothing

## 1.4 Functional Block Diagram

Figure 1. Functional Block Diagram of RF-BM-2340A2(I)

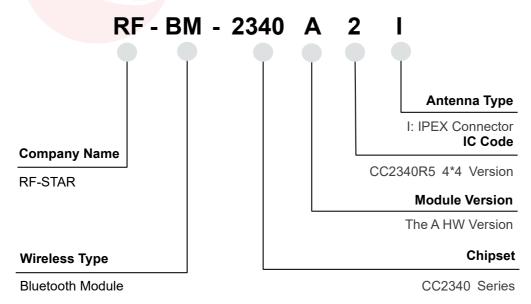

## 1.6 Part Number Conventions

The part numbers are of the form of RF-BM-2340A2(I) where the fields are defined as follows:

Figure 2. Part Number Conventions of RF-BM-2340A2(I)

# **Table of Contents**

| 1.1 Description 1.2 Key Features 1.3 Applications 1.4 Functional Block Diagram 1.6 Part Number Conventions Table of Contents 2 Module Configuration and Functions 2.1 Module Parameters 2.2 Module Pin Diagram 2.3 Pin Functions 2.4 Pin Peripheral Singal Descriptions 3 Specifications 3.1 Recommended Operating Conditions 3.2 Handling Ratings 4 Internal 32.768 kHz Crystal Setting 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design 6.7 Trouble Shooting | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.3 Applications 1.4 Functional Block Diagram 1.6 Part Number Conventions Table of Contents 2 Module Configuration and Functions 2.1 Module Parameters 2.2 Module Pin Diagram 2.3 Pin Functions 2.4 Pin Peripheral Singal Descriptions 3 Specifications 3.1 Recommended Operating Conditions 3.2 Handling Ratings 4 Internal 32.768 kHz Crystal Setting 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification. 6.6 Basic Operation of Hardware Design                                                      | 2  |

| 1.4 Functional Block Diagram 1.6 Part Number Conventions Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2  |

| 1.6 Part Number Conventions Table of Contents.  2 Module Configuration and Functions 2.1 Module Parameters 2.2 Module Pin Diagram 2.3 Pin Functions 2.4 Pin Peripheral Singal Descriptions 3 Specifications 3.1 Recommended Operating Conditions 3.2 Handling Ratings 4 Internal 32.768 kHz Crystal Setting 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                   | 3  |

| Table of Contents.  2 Module Configuration and Functions  2.1 Module Parameters  2.2 Module Pin Diagram  2.3 Pin Functions  2.4 Pin Peripheral Singal Descriptions.  3 Specifications  3.1 Recommended Operating Conditions  3.2 Handling Ratings.  4 Internal 32.768 kHz Crystal Setting  5 Setting of Frequency Offset Register  6 Application, Implementation, and Layout  6.1 Module Photos  6.2 Recommended PCB Footprint  6.3 Schematic Diagram  6.4 Reference Design  6.5 Antenna  6.5.1 Antenna Design Recommendation  6.5.2 Antenna Output Mode Modification  6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin  6.5.4 IPEX Connector Specification  6.6 Basic Operation of Hardware Design                                                                                                         | 4  |

| 2 Module Configuration and Functions 2.1 Module Parameters 2.2 Module Pin Diagram 2.3 Pin Functions 2.4 Pin Peripheral Singal Descriptions 3 Specifications 3.1 Recommended Operating Conditions 3.2 Handling Ratings 4 Internal 32,768 kHz Crystal Setting 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                   | 4  |

| 2.1 Module Parameters. 2.2 Module Pin Diagram. 2.3 Pin Functions. 2.4 Pin Peripheral Singal Descriptions. 3 Specifications. 3.1 Recommended Operating Conditions. 3.2 Handling Ratings. 4 Internal 32.768 kHz Crystal Setting. 5 Setting of Frequency Offset Register. 6 Application, Implementation, and Layout. 6.1 Module Photos. 6.2 Recommended PCB Footprint. 6.3 Schematic Diagram. 6.4 Reference Design. 6.5 Antenna. 6.5.1 Antenna Design Recommendation. 6.5.2 Antenna Output Mode Modification. 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin. 6.5.4 IPEX Connector Specification. 6.6.6 Basic Operation of Hardware Design.                                                                                                                                                                  | 5  |

| 2.2 Module Pin Diagram 2.3 Pin Functions 2.4 Pin Peripheral Singal Descriptions 3 Specifications 3.1 Recommended Operating Conditions 3.2 Handling Ratings 4 Internal 32.768 kHz Crystal Setting 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6.6 Basic Operation of Hardware Design                                                                                                                                                                                                            | 7  |

| 2.3 Pin Functions 2.4 Pin Peripheral Singal Descriptions 3 Specifications 3.1 Recommended Operating Conditions 3.2 Handling Ratings 4 Internal 32.768 kHz Crystal Setting 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                   | 7  |

| 2.4 Pin Peripheral Singal Descriptions.  3 Specifications.  3.1 Recommended Operating Conditions. 3.2 Handling Ratings.  4 Internal 32.768 kHz Crystal Setting. 5 Setting of Frequency Offset Register. 6 Application, Implementation, and Layout. 6.1 Module Photos. 6.2 Recommended PCB Footprint. 6.3 Schematic Diagram. 6.4 Reference Design. 6.5 Antenna. 6.5.1 Antenna Design Recommendation. 6.5.2 Antenna Output Mode Modification. 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin. 6.5.4 IPEX Connector Specification. 6.6.6 Basic Operation of Hardware Design.                                                                                                                                                                                                                                 | 8  |

| 3 Specifications 3.1 Recommended Operating Conditions 3.2 Handling Ratings 4 Internal 32.768 kHz Crystal Setting 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                              | 8  |

| 3.1 Recommended Operating Conditions 3.2 Handling Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10 |

| 3.2 Handling Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 4 Internal 32.768 kHz Crystal Setting  5 Setting of Frequency Offset Register  6 Application, Implementation, and Layout  6.1 Module Photos  6.2 Recommended PCB Footprint  6.3 Schematic Diagram  6.4 Reference Design  6.5 Antenna  6.5.1 Antenna Design Recommendation  6.5.2 Antenna Output Mode Modification  6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin  6.5.4 IPEX Connector Specification  6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                             | 12 |

| 5 Setting of Frequency Offset Register 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                   | 12 |

| 6 Application, Implementation, and Layout 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13 |

| 6.1 Module Photos 6.2 Recommended PCB Footprint 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14 |

| 6.2 Recommended PCB Footprint  6.3 Schematic Diagram  6.4 Reference Design  6.5 Antenna  6.5.1 Antenna Design Recommendation  6.5.2 Antenna Output Mode Modification  6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin  6.5.4 IPEX Connector Specification  6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15 |

| 6.3 Schematic Diagram 6.4 Reference Design 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| 6.4 Reference Design 6.5 Antenna 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15 |

| 6.5 Antenna 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16 |

| 6.5.1 Antenna Design Recommendation 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

| 6.5.2 Antenna Output Mode Modification 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

| 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18 |

| 6.5.4 IPEX Connector Specification 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19 |

| 6.6 Basic Operation of Hardware Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21 |

| 6.7 Trouble Shooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21 |

| 0.7 House Grooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 |

| 6.7.1 Unsatisfactory Transmission Distance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22 |

| 6.7.2 Vulnerable Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

| 6.7.3 High Bit Error Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23 |

## www.rfstariot.com

| 6.8 Electrostatics Discharge Warnings | 23 |

|---------------------------------------|----|

| 6.9 Soldering and Reflow Condition    |    |

| 7 Optional Package Specification      |    |

| 8 Revision History                    | 27 |

| 9 Contact Us                          |    |

# 2 Module Configuration and Functions

## 2.1 Module Parameters

Table 1. Parameters of RF-BM-2340A2(I)

| Chipset                | CC2340R5                                                                     |

|------------------------|------------------------------------------------------------------------------|

| •                      | DCDC mode: 2.2 V ~ 3.8 V, 3.3 V is recommended                               |

|                        | GLDO mode: 1.71 V ~ 3.8 V, 3.3 V is recommended                              |

| Supply Power Voltage   |                                                                              |

|                        | Remark: When set to DCDC mode, if the supply voltage is lower than 2.2 V, it |

| Fraguanay              | will automatically switch to GLDO mode.                                      |

| Frequency              | 2360 MHz ~ 2510 MHz                                                          |

| Maximum Transmit Power | +8.0 dBm                                                                     |

|                        | -102 dBm @ Bluetooth 125 kbps (LE Coded PHY)                                 |

| Receiving Sensitivity  | -99 dBm @ Bluetooth 500 kbps (LE Coded PHY)                                  |

|                        | -96.5 dBm @ Bluetooth 1 Mbps                                                 |

|                        | -92 dBm @ Bluetooth 2 Mbps                                                   |

| GPIO                   | 12                                                                           |

| Flash                  | 512 kB                                                                       |

| ROM                    | 12 kB for bootloader and drivers                                             |

| SRAM                   | 36 kB                                                                        |

|                        | RX current: 5.3 mA                                                           |

|                        | TX current: 5.1 mA @ 0 dBm                                                   |

| Power Consumption      | < 11.0 mA @ 8 dBm                                                            |

| i ower consumption     | MCU (CoreMark): 2.6 mA @ active mode                                         |

|                        | Standby: < 710 nA @RTC, 36 kB RAM                                            |

|                        | Shutdown: 150 nA @ wake-up on pin                                            |

| Support Protocol       | Bluetooth 5.3 Low Energy, ZigBee, Proprietary, SimpleLink TI 15.4-stack      |

| Crystal                | 48 MHz                                                                       |

| Package                | SMT packaging (1.27-mm half-hole pitch stamp stick)                          |

| Dimension              | RF-BM-2340A2: 16.58 mm × 11.19 mm × 2.25 mm                                  |

| Differsion             | RF-BM-2340A2I: 15.20 mm × 11.19 mm × 2.25 mm                                 |

| Type of Antenna        | RF-BM-2340A2: PCB antenna                                                    |

| Type of Afficentia     | RF-BM-2340A2I: IPEX connector or half-hole ANT pin                           |

| Operating Temperature  | -40 °C ~ +85 °C                                                              |

| Storage Temperature    | -40 °C ~ +125 °C                                                             |

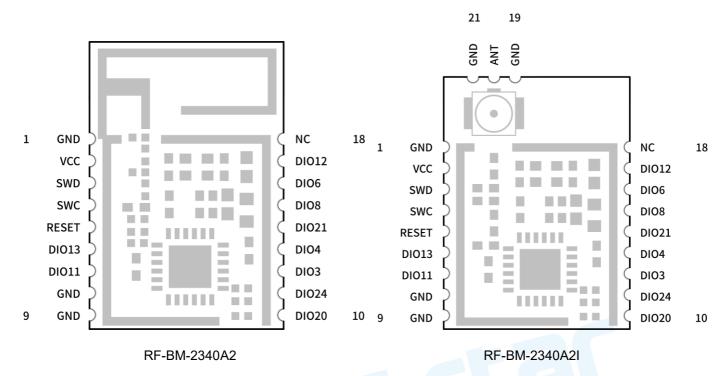

## 2.2 Module Pin Diagram

Figure 3. Pin Diagram of RF-BM-2340A2(I)

## 2.3 Pin Functions

Table 2. Pin Functions of RF-BM-2340A2(I)

| Pin | Name               | Chip Pin    | Function          | Description                                                                               |

|-----|--------------------|-------------|-------------------|-------------------------------------------------------------------------------------------|

| 1   | GND                | GND         | Ground            | Ground                                                                                    |

| 2   | VCC                | VCCS        | VCC               | Power supply: 1.71 V ~ 3.8 V, recommended to 3.3 V                                        |

| 3   | SWDIO <sup>1</sup> | DIO16_SWDIO | Digital           | GPIO, SWD interface: mode select or SWDIO (JTAG_TMSC), high-drive capability, No floating |

| 4   | SWDCK <sup>1</sup> | DIO17_SWDCK | Digital           | GPIO, SWD interface: clock(JTAG_TCKC), high-drive capability, <b>No floating</b>          |

| 5   | RESET              | RSTN        | Digital           | Reset, active low. Internal pullup.                                                       |

| 6   | DIO13              | DIO13       | Digital           | GPIO                                                                                      |

| 7   | DIO11              | DIO11       | Digital           | GPIO                                                                                      |

| 8   | GND                | GND         | Ground            | Ground                                                                                    |

| 9   | GND                | GND         | Ground            | Ground                                                                                    |

| 10  | DIO20              | DIO20_A11   | Digital or Analog | GPIO, analog capability                                                                   |

| 11  | DIO24              | DIO24_A7    | Digital or Analog | GPIO, analog capability, high-drive capability                                            |

| 12  | DIO3               | DIO3_X32P   | Digital or Analog | GPIO, 32-kHz crystal oscillator pin 1                                                     |

www.rfstariot.com

| 13 | DIO4  | DIO4_X32N | Digital or Analog | GPIO, 32-kHz crystal oscillator pin 2           |

|----|-------|-----------|-------------------|-------------------------------------------------|

| 14 | DIO21 | DIO21_A10 | Digital or Analog | GPIO, analog capability                         |

| 15 | DIO8  | DIO8      | Digital           | GPIO                                            |

| 16 | DIO6  | DIO6_A1   | Digital or Analog | GPIO, analog capability                         |

| 17 | DIO12 | DIO12     | Digital           | GPIO, high-drive capability                     |

| 18 | NC    | NC        | -                 | None connect                                    |

| 19 | GND   | GND       | Ground            | Ground, for RF-BM-2340A2I only                  |

| 20 | ANT   | ANT       | RF                | External ANT output pin, for RF-BM-2340A2I only |

| 21 | GND   | GND       | Ground            | Ground, for RF-BM-2340A2I only                  |

Remark 1: **Floating is prohibited.** SWDIO and SWDCK need to be internally or externally pulled up/down (our module does not have external pull-up/down resistors). Otherwise, leakage current may be caused, resulting in excessive power consumption.

# 2.4 Pin Peripheral Singal Descriptions

Table 3. Pin Peripheral Singal Description of RF-BM-2340A2(I)

| Function  | Singal Name    | Module                       | Chip Pin    | Signal                     | Description                            |

|-----------|----------------|------------------------------|-------------|----------------------------|----------------------------------------|

|           |                | Pin<br>DIO13                 | DIO13       | Direction                  |                                        |

|           |                | DIO17                        | DIO17_SWDCK |                            |                                        |

|           | UART0TXD       | DIO20                        | DIO20_A11   | 0                          | LIADTO TV dete                         |

|           | 5,4,4,6,7,6    | DIO4                         | DIO4_X32N   |                            | UART0 TX data                          |

|           |                | DIO6                         | DIO6_A1     |                            |                                        |

| UART      |                | DIO12                        | DIO12       |                            |                                        |

|           | UART0RXD       | DIO16                        | DIO16_SWDIO | I                          | UART0 RX data                          |

|           |                | DIO20                        | DIO20_A11   |                            | o, ii t i o t i o t data               |

|           | UART0CTS       | DIO21                        | DIO21_A10   | I                          | UART0 clear-to-send input (active low) |

|           | UART0RTS       | DIO8                         | DIO8        | 0                          | UART0 request-to-send (active low)     |

|           | ADC11          | DIO20                        | DIO20_A11   |                            | HP ADC channel 11 input                |

| 400       | ADC10/LPC+     | DIO21                        | DIO21_A10   |                            | HP ADC channel 10 input                |

| ADC       | ADC7/LPC+/LPC- | DC7/LPC+/LPC- DIO24 DIO24_A7 | l           | HP ADC channel 7 input     |                                        |

|           | ADC1           | DIO6                         | DIO6_A1     |                            | ADC channel 6 input                    |

| ADC       | ADC1/AREF+     | DIO6                         | DIO6_A1     | ı                          | HP ADC channel 1 input. ADC external   |

| Reference | ADC I/AREI     | DIOU                         | DIOO_A1     | ı                          | voltage reference, positive terminal   |

|           | GPIO8          | DIO8                         | DIO8        |                            |                                        |

|           | GPIO11         | DIO11                        | DIO11       |                            |                                        |

|           | GPIO12         | DIO12                        | DIO12       |                            |                                        |

|           | GPIO13         | DIO13                        | DIO13       |                            |                                        |

|           | GPIO16         | DIO16                        | DIO16_SWDIO |                            |                                        |

| GPIO      | GPIO17         | DIO17                        | DIO17_SWDCK | I/O                        | General-purpose input or output        |

| OI 10     | GPIO20         | DIO20                        | DIO20_A11   | ,, o Conoral parpose input | General-purpose input of output        |

|           | GPIO21         | DIO21                        | DIO21_A10   |                            |                                        |

|           | GPIO24         | DIO24                        | DIO24_A7    |                            |                                        |

|           | GPIO3          | DIO3                         | DIO3_X32P   |                            |                                        |

|           | GPIO4          | DIO4                         | DIO4_X32N   |                            |                                        |

|           | GPIO6          | DIO6                         | DIO6_A1     |                            |                                        |

Table 4. Pin Peripheral Singal Description of RF-BM-2340A2(I) (Continued 1)

| Function         | Singal Name  | Module | Chip Pin    | Signal    | Description     |

|------------------|--------------|--------|-------------|-----------|-----------------|

| Function         | Siligal Name | Pin    | Chilp Pill  | Direction | Description     |

|                  |              | DIO8   | DIO8        |           |                 |

|                  | SPI0SCLK     | DIO17  | DIO17_SWDCK | I/O       | SPI clock       |

|                  |              | DIO24  | DIO24_A7    |           |                 |

|                  |              | DIO11  | DIO11       |           |                 |

|                  |              | DIO12  | DIO12       |           |                 |

|                  | SPI0POCI     | DIO13  | DIO13       | I/O       | SPI POCI (MISO) |

| SPI              |              | DIO20  | DIO20_A11   |           |                 |

| 3PI              |              | DIO21  | DIO21_A10   |           |                 |

|                  | SPIOCSN      | DIO11  | DIO11       | I/O       |                 |

|                  |              | DIO6   | DIO6_A1     |           | SPI chip select |

|                  | SPI0PICO     | DIO12  | DIO12       | I/O       |                 |

|                  |              | DIO13  | DIO13       |           |                 |

|                  |              | DIO16  | DIO16_SWDIO |           | SPI PICO (MOSI) |

|                  |              | DIO4   | DIO4_X32N   |           |                 |

|                  |              | DIO17  | DIO17_SWDCK |           |                 |

|                  | I2C0SCL      | DIO24  | DIO24_A7    | I/O       | I2C clock data  |

| l <sup>2</sup> C |              | DIO6   | DIO6_A1     |           |                 |

| 1-6              |              | DIO8   | DIO8        |           |                 |

|                  | I2C0SDA      | DIO12  | DIO12       | I/O       | I2C data        |

|                  |              | DIO16  | DIO16_SWDIO |           |                 |

## 3 Specifications

## 3.1 Recommended Operating Conditions

The functional operation does not guarantee performance beyond the limits of the conditional parameter values in the table below. Long-term work beyond this limit will affect the reliability of the module more or less.

Table 5. Recommended Operating Conditions of RF-BM-2340A2(I)

| Items                    | Condition | Min. | Тур. | Max. | Unit       |

|--------------------------|-----------|------|------|------|------------|

| Operating Supply Voltage | 1         | 1.71 | 3.3  | 3.8  | V          |

| Operating Temperature    | 1         | -40  | +25  | +85  | $^{\circ}$ |

## 3.2 Handling Ratings

Table 6. Handling Ratings of RF-BM-2340A2(I)

| 10010 0.1101                        | Idining Mattings of the Bivi |      |       |      |            |

|-------------------------------------|------------------------------|------|-------|------|------------|

| Items                               | Condition                    | Min. | Тур.  | Max. | Unit       |

| Storage Temperature                 | Tstg                         | -40  | +25   | +125 | $^{\circ}$ |

| Human Body Model                    | НВМ                          |      | ±1000 |      | V          |

| Moisture Sensitivity Level          |                              |      | 3     |      |            |

| Charged Dev <mark>ice Mo</mark> del |                              |      | ±500  |      | V          |

RCOSC as follows:

## 4 Internal 32.768 kHz Crystal Setting

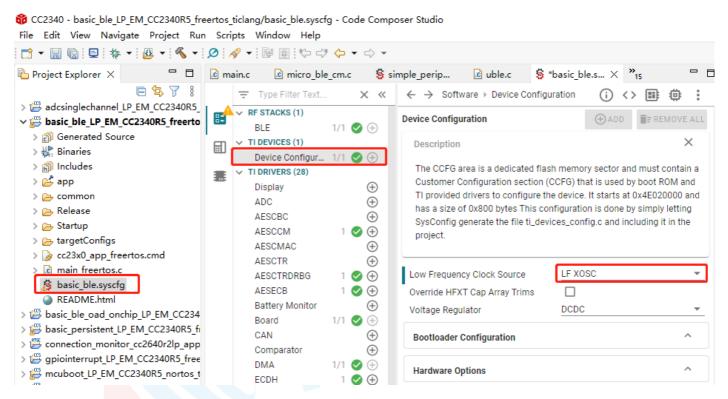

The module hardware is without an external 32.768 kHz crystal by default. However, the SDK adopts the external 32.768 kHz crystal by default, pls see the details below:

Therefore, in or<mark>der no problem during debugging</mark>, pls modify the default crystal setting to the internal crystal LF

## **5 Setting of Frequency Offset Register**

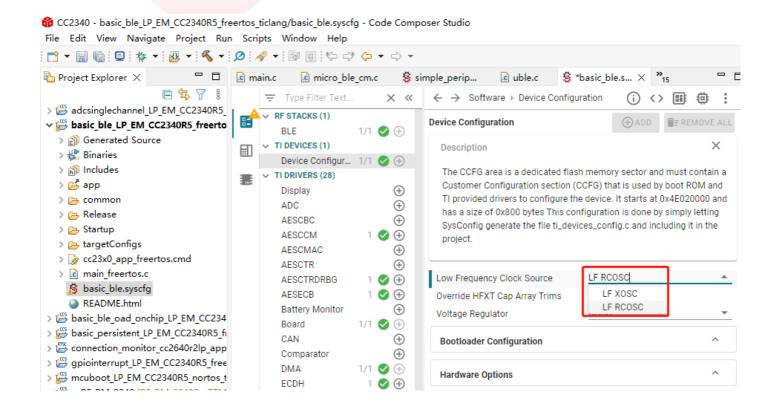

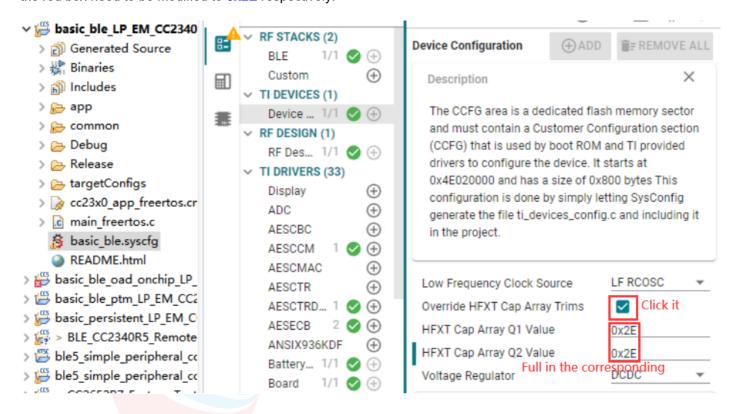

The SDK setting of the frequency offset register can be regarded as the auxiliary setting for modifying the frequency offset for the RF-BM-2340A2(I) hardware RF part. The configuration method is shown in the figure below. The values in the red box need to be modified to **0x2E** respectively:

# 6 Application, Implementation, and Layout

## **6.1 Module Photos**

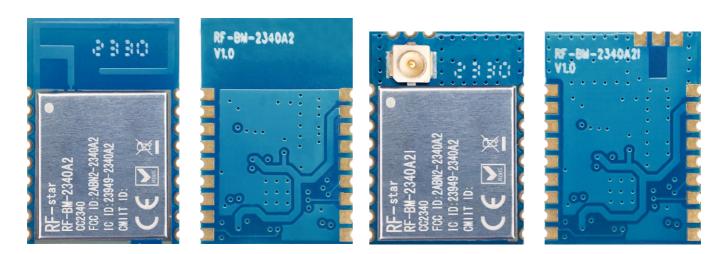

RF-BM-2340A2 RF-BM-2340A2I

Figure 3. Photos of RF-BM-2340A2(I)

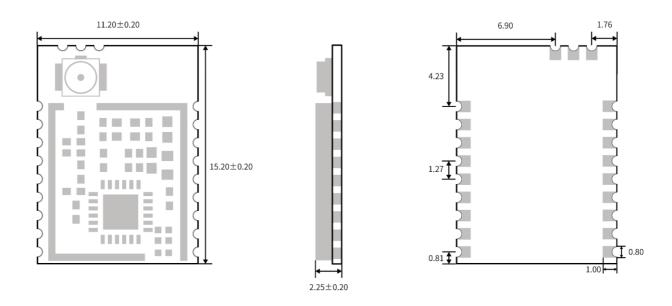

# **6.2 Recommended PCB Footprint**

RF-BM-2340A2

RF-BM-2340A2I

Figure 4. Recommended PCB Footprint of RF-BM-2340A2(I)

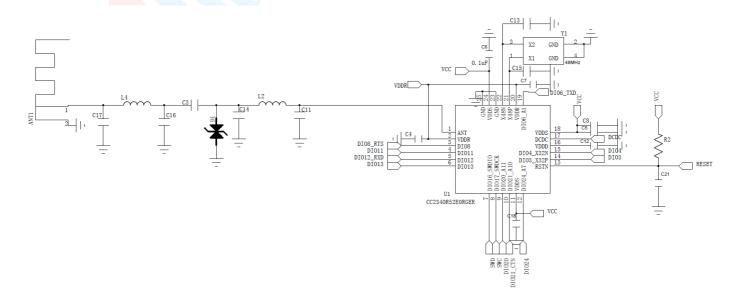

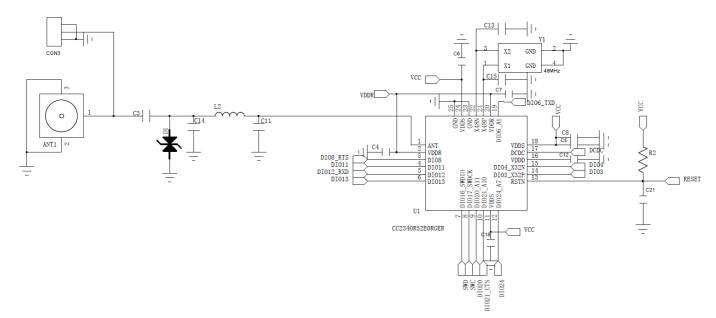

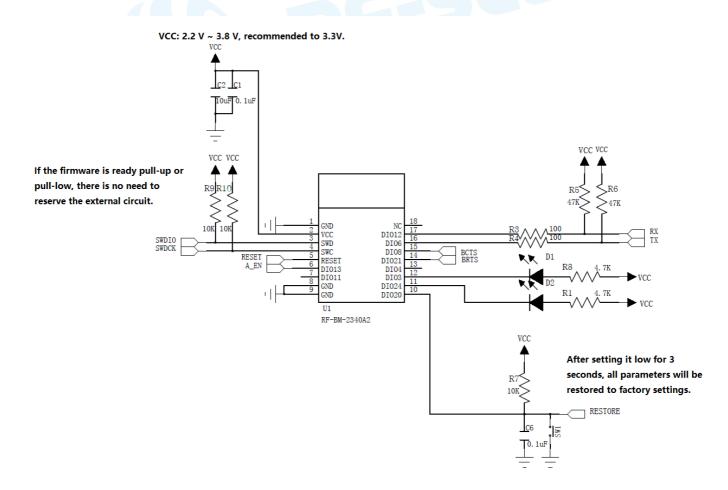

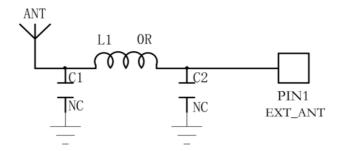

# 6.3 Schematic Diagram

RF-BM-2340A2

RF-BM-2340A2I

Figure 5. Schematic Diagram of RF-BM-2340A2(I)

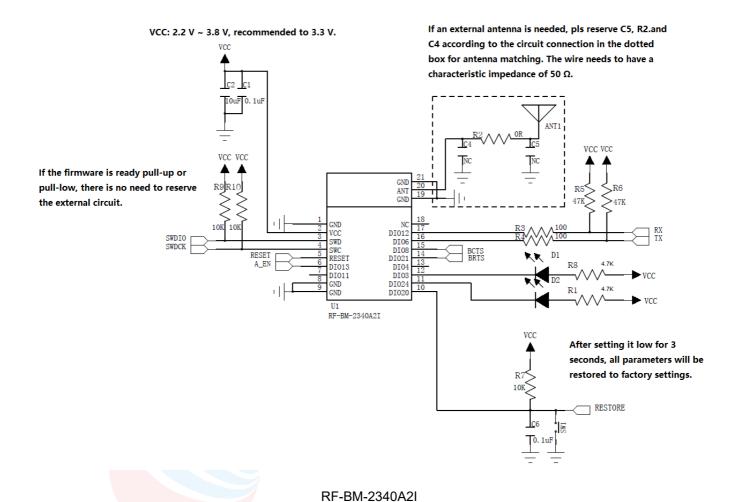

## 6.4 Reference Design

RF-BM-2340A2

Figure 5. Reference Design of RF-BM-2340A2(I)

## 6.5 Antenna

## 6.5.1 Antenna Design Recommendation

- 1. The antenna installation structure has a great influence on the module performance. It is necessary to ensure the antenna is exposed and preferably vertically upward. When the module is installed inside of the case, a high-quality antenna extension wire can be used to extend the antenna to the outside of the case.

- 2. The antenna must not be installed inside the metal case, which will cause the transmission distance to be greatly weakened.

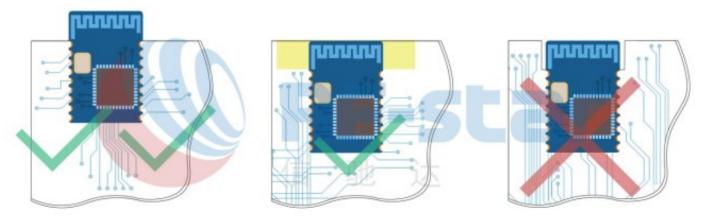

- 3. The recommendation of antenna layout.

The inverted-F antenna position on PCB is free-space electromagnetic radiation. The location and layout of the antenna are key factors to increase the data rate and transmission range.

Therefore, the layout of the module antenna location and routing is recommended as follows:

(1) Place the antenna on the edge (corner) of the PCB.

- (2) Make sure that there is no signal line or copper foil in each layer below the antenna.

- (3) It is best to hollow out the antenna position in the following figure to ensure that the S11 of the module is minimally affected.

Figure 4. Recommendation of Antenna Layout

Note: The hollow-out position is based on the antenna used.

## 6.5.2 Antenna Output Mode Modification

RF-BM-2340A2I has two antenna output modes. One is an IPEX connector and the other is a stamp half-hole output (ANT pin, see pin function table for details).

The default delivery is the *IPEX connector*. If you want to use the external antenna by the ANT pin, just connect the external antenna to the ANT pin.

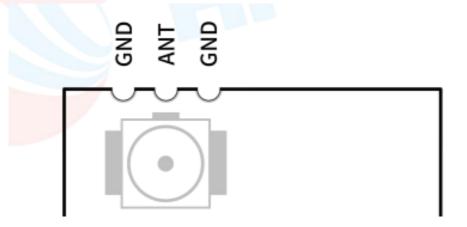

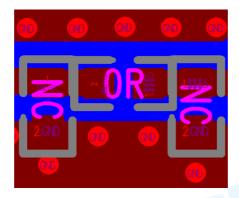

## 6.5.3 External Antenna Design Recommendation of the Half-Hole ANT Pin

1. A  $\Pi$ -type matching circuit is reserved for the antenna, and 50  $\Omega$  impedance control is performed on the RF traces. The traces are as short as possible, and 135° or arc traces are used as much as possible. No vias are used to change layers. More GND vias are placed around the RF traces.

Figure 5. Reference Design of the External Antenna

Figure 6. Reference Design of the External Antenna Traces

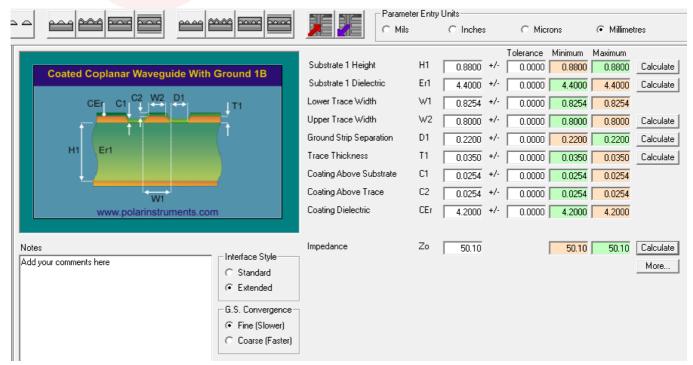

2. The RF trace width and copper-clad spacing can be calculated by SI9000 software, and the impedance is controlled to 50  $\Omega$  according to the actual board thickness, number of layers, plate, dielectric thickness, dielectric constant, copper thickness, line width, line spacing, and solder mask thickness.

Example: FR4 is a double-layer board with a thickness of 1.0 mm. Through calculation, the width of the trace is 0.8254 mm, and the spacing between traces and copper is 0.22 mm.

Figure 7. SI9000 Impedance Calculation Diagram

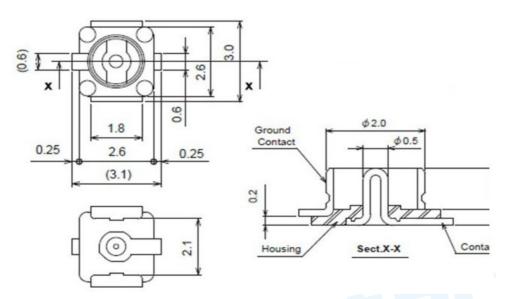

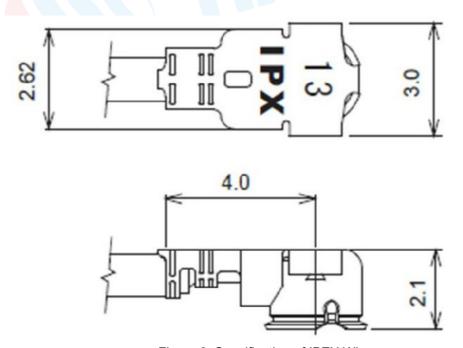

## **6.5.4 IPEX Connector Specification**

RF-BM-2340A2I module is integrated with the IPEX version 1 antenna seat, the specification of the antenna seat is as follows:

Figure 8. Specification of Antenna Seat

The specification of the IPEX wire end is as follows:

Figure 9. Specification of IPEX Wire

## 6.6 Basic Operation of Hardware Design

1. It is recommended to offer the module a DC stabilized power supply, a tiny power supply ripple coefficient, and reliable ground. Please pay attention to the correct connection between the positive and negative poles of the power

- supply. Otherwise, the reverse connection may cause permanent damage to the module.

- 2. Please ensure the supply voltage is between the recommended values. The module will be permanently damaged if the voltage exceeds the maximum value. Please ensure a stable power supply and no frequently fluctuating voltage.

- 3. When designing the power supply circuit for the module, it is recommended to reserve more than 30% of the margin, which is beneficial to the long-term stable operation of the whole machine. The module should be far away from the power electromagnetic, transformer, high-frequency wiring, and other parts with large electromagnetic interference.

- 4. The bottom of the module should avoid high-frequency digital routing, high-frequency analog routing, and power routing. If it has to route the wire on the bottom of the module, for example, it is assumed that the module is soldered to the Top Layer, the copper must be spread on the connection part of the top layer and the module, and be close to the digital part of the module and routed in the Bottom Layer (all copper is well-grounded).

- 5. Assuming that the module is soldered or placed in the Top Layer, it is also wrong to randomly route the Bottom Layer or other layers, which will affect the spurs and receiving sensitivity of the module to some degree.

- 6. Assuming that there are devices with large electromagnetic interference around the module, which will greatly affect the module performance. It is recommended to stay away from the module according to the strength of the interference. If circumstances permit, appropriate isolation and shielding can be done.

- 7. Assuming that there are routings of large electromagnetic interference around the module (high-frequency digital, high-frequency analog, power routings), which will also greatly affect the module performance. It is recommended to stay away from the module according to the strength of the interference. If circumstances permit, appropriate isolation and shielding can be done.

- 8. It is recommended to stay away from devices whose TTL protocol is the same 2.4 GHz physical layer, for example, USB 3.0.

## 6.7 Trouble Shooting

## 6.7.1 Unsatisfactory Transmission Distance

- When there is a linear communication obstacle, the communication distance will be correspondingly weakened.

Temperature, humidity, and co-channel interference will lead to an increase in the communication packet loss rate.

The performance of ground absorption and reflection of radio waves will be poor when the module is tested close to the ground.

- 2. Seawater has a strong ability to absorb radio waves, so the test results by the seaside are poor.

- 3. The signal attenuation will be very obvious if there is metal near the antenna or if the module is placed inside the metal shell.

- 4. The incorrect power register set or the high data rate in the open air may shorten the communication distance. The higher the data rate, the closer the distance.

- The low voltage of the power supply is lower than the recommended value at ambient temperature, and the lower the voltage, the smaller the power is.

- 6. The unmatchable antennas and modules or the poor quality of the antenna will affect the communication distance.

#### 6.7.2 Vulnerable Module

- Please ensure the supply voltage is between the recommended values. The module will be permanently damaged

if the voltage exceeds the maximum value. Please ensure a stable power supply and no frequently fluctuating

voltage.

- 2. Please ensure the anti-static installation and the electrostatic sensitivity of high-frequency devices.

- 3. Due to some humidity-sensitive components, please ensure the suitable humidity during installation and application.

If there is no special demand, it is not recommended to use at too high or too low temperature.

## 6.7.3 High Bit Error Rate

- There are co-channel signal interferences nearby. It is recommended to be away from the interference sources or modify the frequency and channel to avoid interferences.

- 2. The unsatisfactory power supply may also cause a garble. It is necessary to ensure the power supply's reliability.

- 3. If the extension wire or feeder wire is of poor quality or too long, the bit error rate will be high.

## 6.8 Electrostatics Discharge Warnings

The module will be damaged by the discharge of static. RF-star suggests that all modules should follow the 3 precautions below:

- 1. According to the anti-static measures, bare hands are not allowed to touch modules.

- 2. Modules must be placed in anti-static areas.

- 3. Take the anti-static circuitry (when inputting HV or VHF) into consideration in product design. Static may result in the degradation in performance of the module, even causing failure.

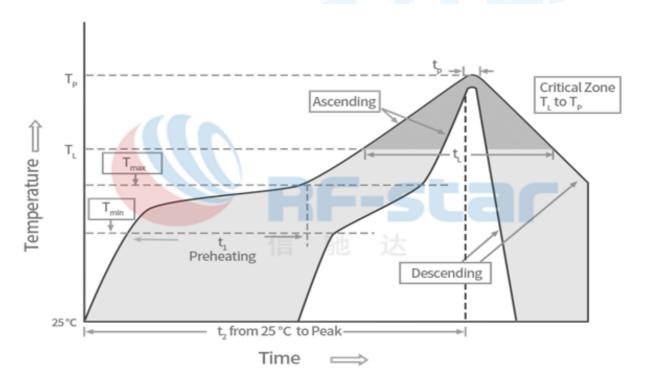

## 6.9 Soldering and Reflow Condition

- 1. Heating method: Conventional Convection or IR/convection.

- 2. Solder paste composition: Sn96.5/Ag3.0/Cu0.5

- 3. Allowable reflow soldering times: 2 times based on the following reflow soldering profile.

- 4. Temperature profile: Reflow soldering shall be done according to the following temperature profile.

- Peak temperature: 245 ℃.

Table 7. Temperature Table of Soldering and Reflow

| Profile Feature                                                           | Sn-Pb Assembly | Pb-Free Assembly       |

|---------------------------------------------------------------------------|----------------|------------------------|

| Solder Paste                                                              | Sn63 / Pb37    | Sn96.5 / Ag3.0 / Cu0.5 |

| Min. Preheating Temperature (T <sub>min</sub> )                           | 100 ℃          | 150 ℃                  |

| Max. Preheating Temperature (T <sub>max</sub> )                           | 150 ℃          | 200 ℃                  |

| Preheating Time (T <sub>min</sub> to T <sub>max</sub> ) (t <sub>1</sub> ) | 60 s ~ 120 s   | 60 s ~ 120 s           |

| Average Ascend Rate (T <sub>max</sub> to T <sub>p</sub> )                 | Max. 3 °C/s    | Max. 3 °C/s            |

| Liquid Temperature (T <sub>L</sub> )                                      | 183 ℃          | 217 ℃                  |

| Time above Liquidus (t∟)                                                  | 60 s ~ 90 s    | 30 s ~ 90 s            |

| Peak Temperature (T <sub>p</sub> )                                        | 220 ℃ ~235 ℃   | 230 ℃ ~250 ℃           |

| Average Descend Rate (T <sub>p</sub> to T <sub>max</sub> )                | Max. 6 ℃/s     | Max. 6 °C/s            |

| Time from 25 ℃ to Peak Temperature (t₂)                                   | Max. 6 minutes | Max. 8 minutes         |

| Time of Soldering Zone (t <sub>P</sub> )                                  | 20±10 s        | 20±10 s                |

Figure 10. Recommended Reflow for Lead-Free Solder

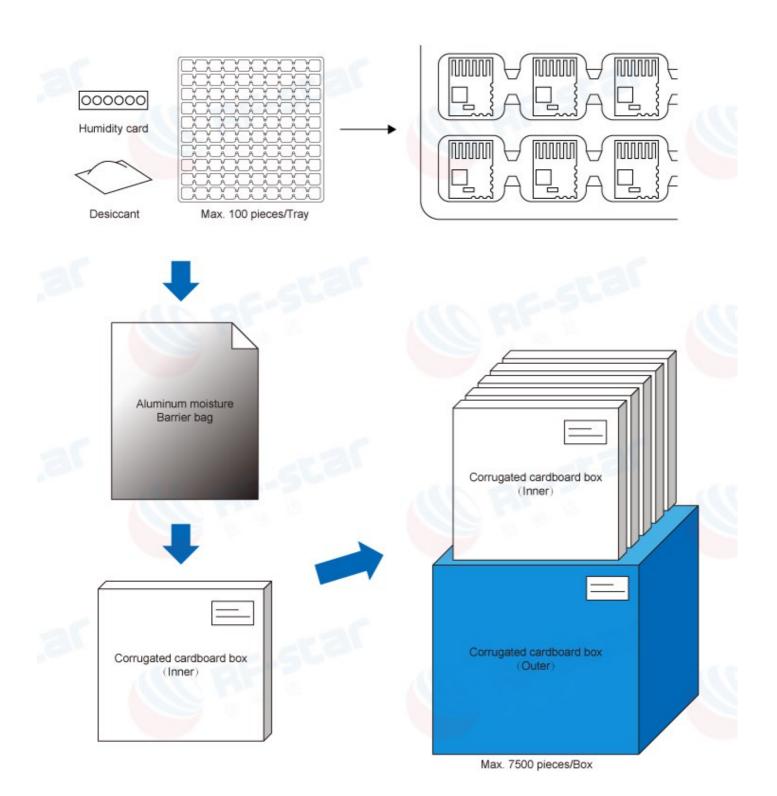

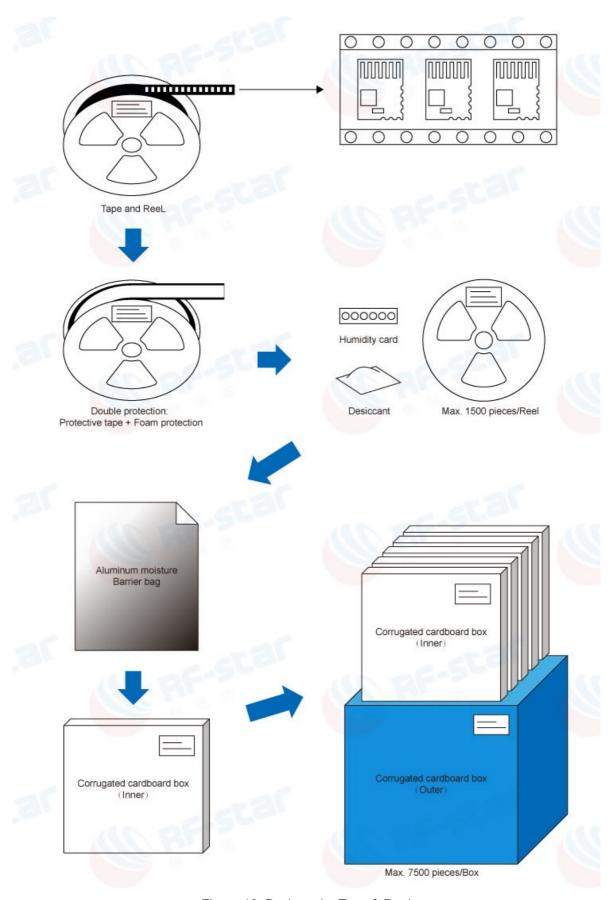

# 7 Optional Package Specification

The default package method is **by tray**. If you need the modules to be shipped by tape & reel, pls contact us in advance.

Figure 11. Default Package by Tray

Figure 12. Package by Tape & Reel

# **8 Revision History**

| Date       | Version No. | Description                                                                                                                              |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 2023.09.01 | V1.0        | The initial version is released.                                                                                                         |

| 2024.05.21 | V1.0        | Add the reference design.  Update the Recommended PCB Footprint.                                                                         |

| 2024.06.06 | V1.1        | Add the setting of the frequency offset register.  Add the no floating specification of the debugging IOs.  Update the reference design. |

## Note:

- 1. The document will be optimized and updated from time to time. Before using this document, please make sure it is the latest version.

- 2. To obtain the latest document, please download it from the official website: www.rfstariot.com and www.szrfstar.com.

## 9 Contact Us

## SHENZHEN RF-STAR TECHNOLOGY CO., LTD.

## Shenzhen HQ:

Add.: Room 502 ~ 503, Podium Building No. 12, Shenzhen Bay Science and Technology Ecological Park, Nanshan District, Shenzhen, Guangdong, China, 518063

Tel.: 86-755-8632 9829

## Chengdu Branch:

Add.: N2-1604, Global Center, North No. 1700, Tianfu Avenue, Hi-Tech District, Chengdu, Sichuan, China, 610095

Tel.: 86-28-8692 5399

Email: sunny@szrfstar.com, sales@szrfstar.com Web.: <u>www.rfstariot.com</u>, www.szrfstar.com